JEDEC Solid State Technology Association, pemimpin global dalam pengembangan standar industri mikroelektronika, baru saja mengumumkan rencana standar baru untuk modul memori canggih. Standar ini dirancang untuk mendukung generasi berikutnya dari komputasi berkinerja tinggi dan aplikasi kecerdasan buatan (AI).

Pada 22 Juli 2024, JEDEC mengungkapkan detail utama tentang standar baru untuk DDR5 Multiplexed Rank Dual Inline Memory Modules (MRDIMM) dan Compression-Attached Memory Module (CAMM) untuk LPDDR6. Kedua standar ini diharapkan dapat merevolusi industri dengan peningkatan bandwidth dan kapasitas memori yang belum pernah ada sebelumnya.

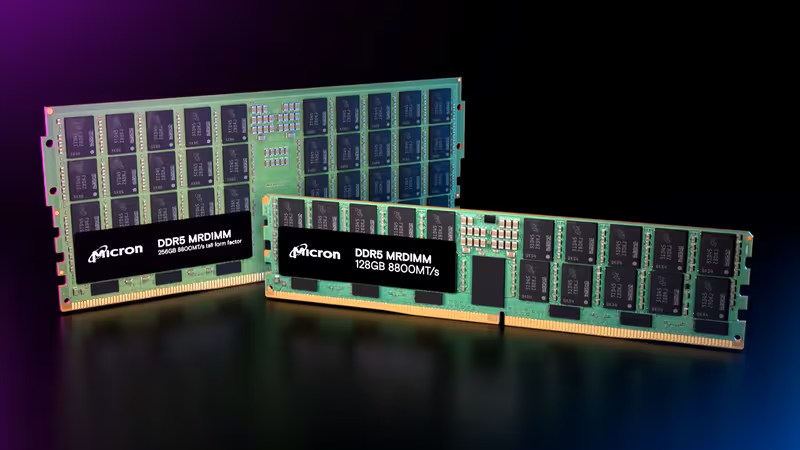

DDR5 MRDIMM: DDR5 MRDIMM menawarkan desain modul baru yang inovatif dan efisien untuk meningkatkan kecepatan transfer data dan kinerja sistem secara keseluruhan. Teknologi multiplexing memungkinkan beberapa sinyal data digabungkan dan ditransmisikan melalui satu saluran, sehingga meningkatkan bandwidth tanpa memerlukan koneksi fisik tambahan. Fitur utama lainnya termasuk kompatibilitas platform dengan RDIMM, penggunaan komponen standar DDR5 DIMM, dan skalabilitas I/O yang efisien menggunakan proses logika RCD/DB.

MRDIMM diharapkan dapat memberikan bandwidth puncak hingga dua kali lipat dari DRAM asli, memungkinkan aplikasi untuk melampaui kecepatan data saat ini dan mencapai tingkat kinerja baru. Standar ini juga mempertahankan kapasitas, keandalan, ketersediaan, dan fitur layanan (RAS) yang sama dengan JEDEC RDIMM. Komite JEDEC bertujuan untuk menggandakan bandwidth menjadi 12,8 Gbps dan meningkatkan kecepatan pin. MRDIMM dirancang untuk mendukung lebih dari dua rank dan menggunakan komponen standar DDR5 DIMM, memastikan kompatibilitas dengan sistem RDIMM konvensional.

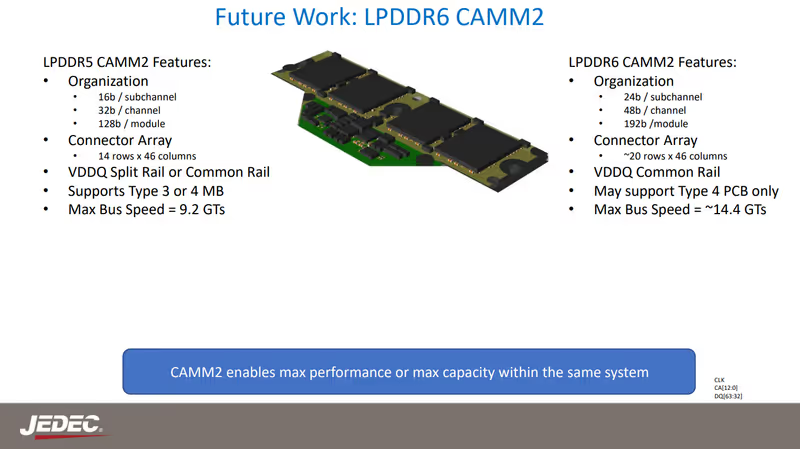

LPDDR6 CAMM: Sebagai tindak lanjut dari standar JESD318 CAMM2 Memory Module, JC-45 sedang mengembangkan modul CAMM generasi berikutnya untuk LPDDR6 yang menargetkan kecepatan maksimum lebih dari 14,4 GT/s. Modul ini juga akan menawarkan subchannel 24-bit, channel 48-bit, dan array konektor. Kedua proyek ini sedang dikembangkan dalam Komite JC-45 untuk Modul DRAM.

LPCAMM juga akan mengalami perubahan besar. Konektor LPCAMM akan bertambah dari 14 baris pin menjadi mungkin 20 baris. Perubahan ini diperlukan untuk mengakomodasi bus memori yang lebih lebar dari LPDDR6. Meskipun perubahan ini signifikan, ini bukan hal yang tidak terduga dalam teknologi memori baru.

JEDEC mendorong perusahaan untuk bergabung dan membantu membentuk masa depan standar JEDEC. Keanggotaan memberikan akses ke proposal pra-publikasi dan wawasan awal tentang proyek aktif seperti MRDIMM. Standar JEDEC dapat berubah selama dan setelah proses pengembangan, termasuk penolakan oleh Dewan Direksi JEDEC. Pengumuman JEDEC tentang standar baru LPDDR6 CAMM dan DDR5 MRDIMM menunjukkan komitmen mereka untuk terus mendorong batas teknologi memori.

Sumber: JEDEC